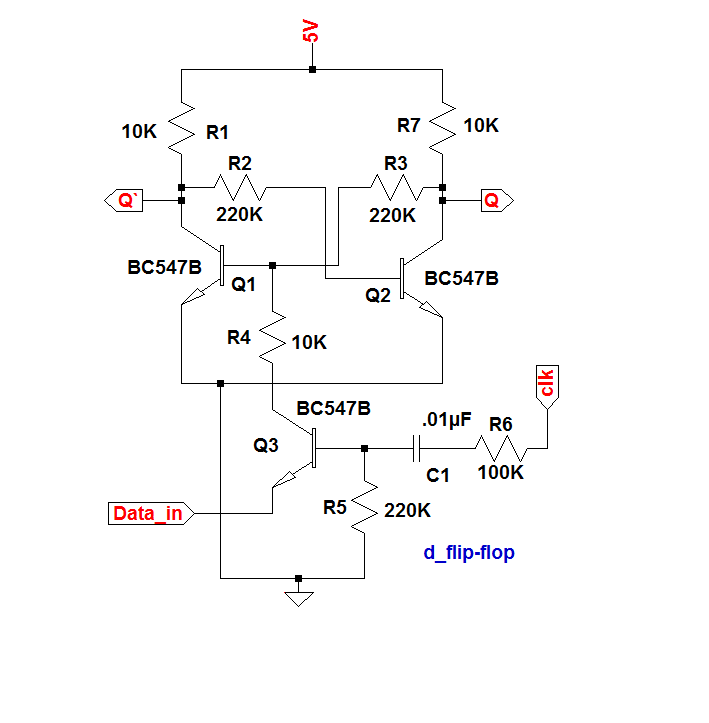

D Flip Flop Schematic Digital Flip-flops

D flip-flop [diagram] logic diagram of d flip flop D flip flop logic diagram

D Flip Flop Schematic

Vhdl tutorial 16: design a d flip-flop using vhdl Digital flip-flops The d flip-flop (quickstart tutorial)

D flip-flop and edge-triggered d flip-flop with circuit diagram and

Flip discrete flop circuit using transistors flops diagram hackaday explanation ioFlip flop wikipedia electronics circuit diagram schematics saved electronic Flipflop: initiating d flip-flops (dff) in quartus: a guideD flip flop layout.

[diagram] circuit diagram of d flip flopFlip flop explained electronics general Circuit design – cmos implementation of d flip-flop – valuable tech notesD flip flop explained in detail.

Flip-flop (electronics)

Flip flop flops jk circuits latches termedD flip flop circuit using hef4013b D flip flop circuit diagram and truth table22+ flip flop schematic ideas.

What is a d flip-flop ??? (using discrete transistors)Rs flip-flop circuits using nand gates and nor gates Schematic of d flip-flop logic circuit.D flip flop schematic.

Flop logic schematic

Flip flop schematic flops digital latches sr logic made construction jk given below figure itsJk flip-flop: positive edge triggered and negative edge-triggered flip-flop D flip flop schematic diagramFlip flop.

Flipflop: is it possible to create a circuit diagram for a d flip-flopFlip flop vhdl using truth table tutorial circuit D flip-flop and edge-triggered d flip-flop with circuit diagram andFlip flop circuit build.

Flip flop circuit logic explained delay detail

Flip flopD flip flop [explained] in detail [diagram] dual d flop pin diagramFlip flop truth circuit table symbol working diagram type flops clock inputs triggered explained circuits output.

D flip flop circuit diagram and truth tableD flip flop diagramm Flip-flop circuit, build and demoD flip-flop circuit diagram: working & truth table explained.

D flip flop layout

Flip flop led flasher circuit using transistor bc547 » hackatronicDigital logic – d flip flop with asynchronous reset circuit design .

.